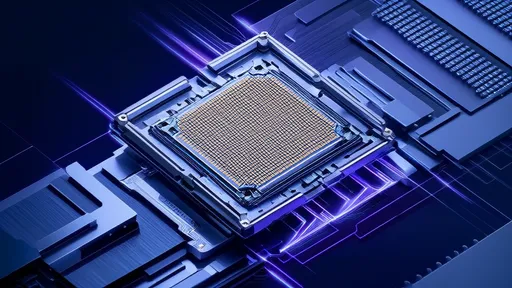

The concept of secure boot chains has become a cornerstone in modern microcontroller unit (MCU) design, particularly as embedded systems grow more complex and interconnected. In an era where cyber threats are increasingly sophisticated, ensuring the integrity of firmware and software from the moment of power-on is no longer optional—it's a critical requirement. MCU manufacturers and system designers are now prioritizing secure boot mechanisms to defend against unauthorized code execution, malware injection, and other low-level attacks that could compromise entire systems.

At its core, a secure boot chain establishes a sequence of trust that begins with immutable hardware and extends through each subsequent software layer. The process typically starts with a hardware-rooted trust anchor, often a cryptographic key burned into the MCU during manufacturing. This key serves as the foundation for verifying the authenticity and integrity of the initial bootloader, which in turn validates the next stage of firmware. By creating this hierarchical verification process, the MCU ensures that only trusted, unaltered code can execute, effectively closing the door to many types of firmware-based attacks.

Hardware-based security features have become increasingly sophisticated in modern MCUs to support robust secure boot implementations. Many processors now include dedicated security subsystems such as Trusted Execution Environments (TEEs), hardware cryptographic accelerators, and one-time programmable (OTP) memory for storing sensitive keys. These features work in concert to establish a hardware root of trust that persists even if higher-level software components become compromised. The physical unclonable functions (PUFs) found in some advanced MCUs take this a step further by deriving unique device-specific keys from physical characteristics of the silicon itself.

The evolution of secure boot chains reflects the growing recognition that security must be baked into the hardware from the ground up. Early implementations often relied on simple checksum verification or basic signature checking, but contemporary approaches employ sophisticated cryptographic techniques including asymmetric cryptography, hash trees, and certificate chains. These methods provide not only verification of code authenticity but also protection against rollback attacks, where an adversary might attempt to revert the system to a vulnerable earlier version of firmware.

Implementation challenges remain despite the clear security benefits of secure boot chains. One significant hurdle involves balancing security requirements with real-world operational constraints. Resource-constrained MCUs must carefully manage the computational overhead of cryptographic operations during boot, as excessive delays may be unacceptable in time-sensitive applications. Additionally, secure boot implementations must account for legitimate firmware updates while maintaining protection against unauthorized modifications—a delicate balance that requires careful key management and version control mechanisms.

The supply chain aspects of secure boot present another layer of complexity. Establishing trust from silicon fabrication through final product deployment requires coordinated security measures at every stage. MCU manufacturers must implement secure key provisioning processes, while device makers need robust systems for managing their own keys and certificates. This end-to-end security approach has given rise to specialized secure provisioning services and hardware security modules (HSMs) designed specifically for IoT and embedded device manufacturing environments.

Looking ahead, the future of MCU secure boot chains will likely involve even tighter integration with system-wide security architectures. Concepts like confidential computing, where data remains encrypted even during processing, may influence future boot chain designs. Similarly, the growing adoption of post-quantum cryptography standards will necessitate updates to the cryptographic primitives used in secure boot implementations. As attack techniques continue to evolve, so too must the defenses that secure boot chains provide, ensuring that MCU-based systems can withstand emerging threats throughout their operational lifetimes.

Industry standards and certifications have emerged to help guide and validate secure boot implementations. Frameworks like Common Criteria, FIPS 140-3, and ISA/IEC 62443 provide structured approaches to evaluating the security of boot processes. These standards not only help manufacturers demonstrate compliance with security requirements but also give system integrators confidence in the components they select. The automotive industry's adoption of ISO/SAE 21434 for cybersecurity risk management has particularly driven advancements in secure boot technology for vehicle ECUs.

The role of secure boot chains extends beyond just preventing malicious attacks—it also serves as a foundation for device identity and attestation. In connected systems, the ability to cryptographically verify that a device booted with authorized software enables trust establishment in larger networks. This capability is particularly valuable in zero-trust architectures and industrial IoT deployments where devices must prove their integrity before being granted network access or permitted to participate in critical operations.

As the Internet of Things continues to expand, bringing MCUs into increasingly sensitive and safety-critical applications, the importance of robust secure boot chains will only intensify. From smart cities to medical devices to industrial control systems, the ability to ensure firmware integrity from the first clock cycle has become a fundamental requirement rather than a luxury feature. This shift represents a maturation of embedded systems security, acknowledging that in our interconnected world, the weakest link in the security chain could have consequences far beyond any individual device.

By /Jul 29, 2025

By /Jul 29, 2025

By /Jul 29, 2025

By /Jul 29, 2025

By /Jul 29, 2025

By /Jul 29, 2025

By /Jul 29, 2025

By /Jul 29, 2025

By /Jul 29, 2025

By /Jul 29, 2025

By /Jul 29, 2025

By /Jul 29, 2025

By /Jul 29, 2025

By /Jul 29, 2025

By /Jul 29, 2025

By /Jul 29, 2025

By /Jul 29, 2025

By /Jul 29, 2025

By /Jul 29, 2025

By /Jul 29, 2025